先写在前面,就是补一点感觉。在很多半导体芯片的介绍中,我们经常可以看到采用了多少纳米工艺,久而久之我们就习惯了。它不仅仅是一个参数,也不重要。时隔多年,我们对FinFET和FD-SOI工艺的了解不能说有多少。那么FinFET到底是什么呢?它的作用是什么?为什么那么多国际大公司趋之若鹜?

FinFET首先是什么?

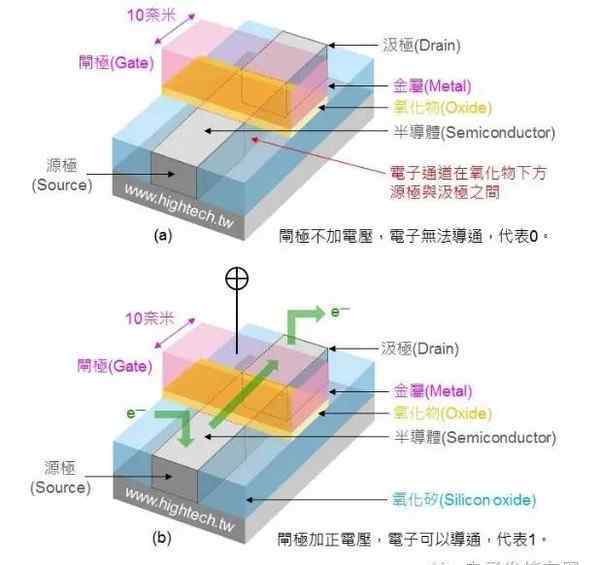

鳍型场效应晶体管,又称鳍型场效应晶体管,是一种新型互补金属氧化物半导体晶体管。FET的全称是“场效应晶体管”,用大家熟悉的“MOS”这个词来解释。MOS的全称是“金属氧化物半导体场效应晶体管(MOSFET)”,其结构如图1所示。左边的灰色区域(硅)称为“源极”,右边的灰色区域(硅)称为“漏极”。中间凸出一块金属(绿色),叫“门”,门下有一层薄薄的氧化物(黄色)。因为中间从上到下依次是金属、氧化物、半导体,所以叫“MOS”。

我们来看看工作原理

FinFET的栅极长度可以小于25nm,未来有望进一步减小到7nm,约为人发宽度的1/10000。由于这种导体技术的突破,未来的芯片设计者有望设计出指甲般大的超级计算机。

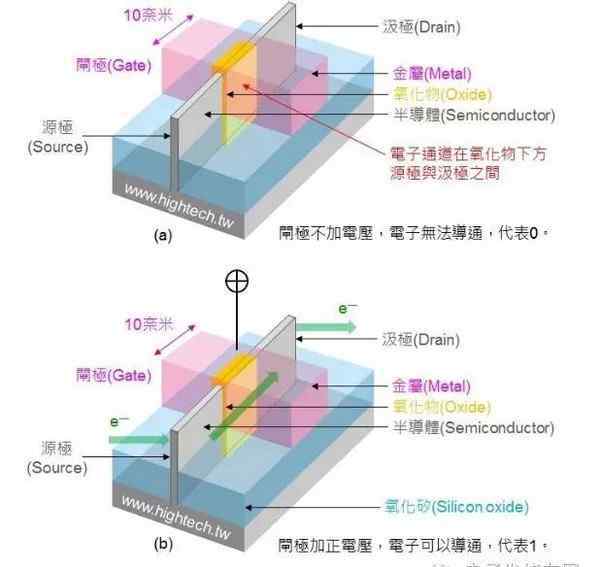

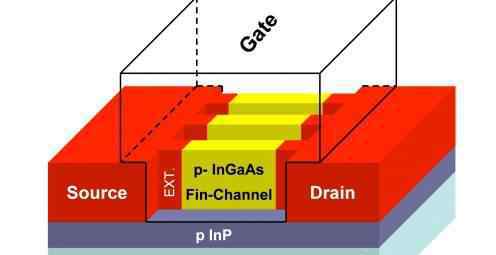

FinFET源自传统标准晶体管的创新设计-场效应晶体管。在传统的晶体管结构中,控制电流通过的栅极只能控制栅极一侧电路的导通和关断,属于平面架构。在FinFET架构中,栅极是类似于鳍的叉形3D架构,可以控制电路两侧电路的通断。这种设计可以大大改善电路控制,降低漏电流,也可以大大缩短晶体管的栅极长度。

补充MOSFET的工作原理

MOSFET的工作原理很简单。电子从左侧源极流入,通过栅极下方的电子通道,从右侧漏极流出。中间的门可以决定是否让电子从下面通过,有点像水龙头的开关,所以叫“门”;电子从源头,也就是电子的源头流入,所以叫“源头”;电子从漏极流出。看《说文解字》里的引子:引流是为了把水引到井里,也就是从这里把电子取出来,所以叫“引流”。

所有大型晶圆代工厂都宣称FinFET技术是他们最先进的技术。英特尔在22纳米节点上使用这种晶体管1,TSMC在16纳米工艺上使用这种晶体管2,三星和全球晶圆厂在14纳米工艺上使用这种晶体管。

与所有其他新技术一样,FinFET工艺涉及到学习如何将其用于设计的成本。由于鳍式场效应晶体管是完全不同的晶体管,问题变成了这种变化是渐进的(典型的学习成本)还是革命性的(显著的学习成本)。

FinFET的新领域

自发明以来,MOSFET结构已经使用了40多年。当栅极长度减小到20纳米以下时,会遇到许多问题。最麻烦的是,栅极长度越短,源极和漏极的距离越近,栅极下的氧化物越薄,电子可能会潜过去,造成“漏电”。另一个更麻烦的问题是,电子能否从源极流向漏极是由栅极电压控制的,但栅极长度越小,栅极与沟道的接触面积越小,即栅极对沟道的影响越小。如何才能维持闸门对通道的影响?

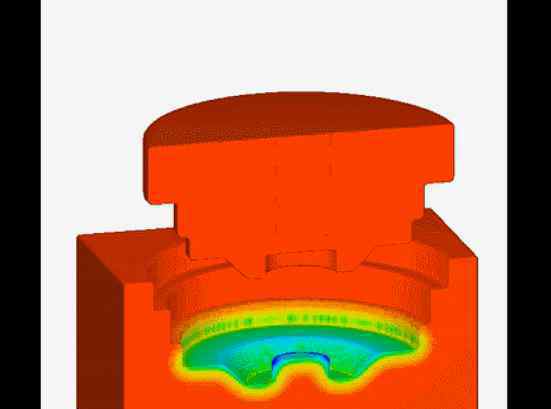

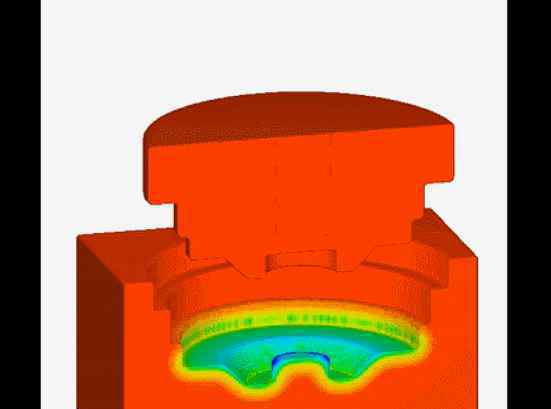

于是,加州大学柏克莱分校的、Tsu-Jae King-Liu、Jeffrey Bokor等三位教授发明了Fin场效应晶体管(FinFET),将原来具有结构的MOSFET变成了3D的FinFET。如图2所示,它被称为“鳍”,因为它的结构非常类似于鳍。

从图中可以看出,将原来的源漏拉成三维板状结构,使源漏之间的沟道变成板状,栅极与沟道的接触面积变大(图2中黄色氧化物与下部的接触面积明显大于图1中红色虚线面积), 从而即使栅极长度减小到小于20纳米,仍保留大的接触面积,这可以控制电子是否可以从源极流向漏极,从而可以更好地控制电流。 同时,

另外,从仿真或IP设计人员的角度来看,以上设计方法(fin由晶圆代工厂实现)并不是首选模型。这些设计师希望获得更多的自由度,以减少泄漏,匹配驱动能力,提高频率响应,并推动电气和几何限制,而这些是固定鳍所不能实现的。这种设计根据其性质是定制的,很多设计师无法控制鳍的数量或大小是非常不舒服的。

对于从28nm或以上跳到FinFET工艺的定制、模拟或IP设计人员来说,这种设计是革命性的,但不一定是字面上的“新改进”。虽然有工具创新来缓解这种转变,但设计方法可能比其习惯的设计方法更严格。利用传统的金属氧化物半导体场效应晶体管技术,这些设计师设计定制的晶体管,包括定制它们的尺寸和方向。对于FinFET,设计者将使用更少的变量实现所需的电气响应。有人怀疑先进的模拟设计能否通过FinFET工艺完成,很多人都讨论过这个问题。答案是肯定的,但是设计方法需要大大改变,可能需要更多的实验。

具有大功率因数的鳍式场效应晶体管和FD-SOI工艺

在我们大多数人的“非黑即白”或“非此即彼”的概念中,半导体厂商要么选择FinFET,要么选择FD-SOI工艺技术;然而,由于TSMC、全球晶圆代工厂(GlobalFoundrie)或三星(Samsung)等晶圆代工厂必须同时提供上述两种处理能力来服务客户,越来越多的半导体制造商也在考虑提供两全其美的解决方案。

FD- SOI工艺需要传感器集成,28 nm节点具备所需的射频和模拟功能,可以让很多可穿戴设备在连接性和低功耗之间达到诱人的平衡。每个节点在40 nm节点和28 nm节点都是FD-SOI,而FinFET则是14~16 nm节点等更高级的节点。在工艺小型化和成本优化方面,我们将看到如何有效利用FD-SOI和FinFET。"

该图显示了如何更好地隔离SOI上的鳍式场效应晶体管,以及无限沟道如何简化工艺步骤

意法半导体选择了FD-SOI而不是FinFET。在前者中,在晶体管(BOX)下面放置一个薄绝缘体,使得未掺杂的沟道完全空耗尽,并且漏电流最小化。然而,FD-SOI的另一个经常被忽略的优点是能够极化BOX以下的衬底,即“正向衬底偏置”。正向衬底偏置在优化功耗和性能之间的权衡方面非常有效,并且通过在操作期间改变偏置电压,设计工程师可以使他们的晶体管在不使用时实现超低功耗,并且在速度正常的关键时刻实现超高性能。

设计师专注于写什么

对于大多数晶圆代工厂,16纳米和14纳米BEOL结构与20纳米节点相同。20nm采用双曝光(DP)4,对设计制造界影响很大。DP促进设计过程的改变,是EDA工具在设计、验证、寄生参数提取和分析方面的催化剂。

DP的挑战最近发生了。三次曝光或多次曝光已经到来,但在现有的FinFET工艺中没有使用。由于BEOL和20纳米一样,设计师需要学习和理解之前工艺的几何变化。

当您第一次看到这些设备时,大多数设计师会问以下问题:

1.怎么设计?

2.一个设备应该包含多少个鳍?

3.翅片尺寸/间距应该是多少?

4.如何获得所需的信息,以了解几何形状和电气性能之间的折衷?

通常,设计人员,尤其是数字设计人员在权衡晶体管结构和电气性能时,会考虑宽度、长度和面积作为参数。FinFET设计的本质可以极大地改变这一切。幸运的是,大多数晶圆代工厂已经考虑到这一点,并开发了一种与20纳米及以上的FinFET工艺相同的设计方法。

掌握FinFET技术意味着掌握市场

商业化的FinFET是从英特尔公司引进的,用于其22纳米节点的过程中。英特尔酷睿i7-3770之后的22纳米处理器都采用了FinFET技术。由于鳍片场效应管具有低功耗和小面积的优势,TSMC和其他主要半导体晶圆厂也推出了自己的鳍片场效应管晶体管,为未来的移动处理器提供更快、更节能的处理器。

简而言之,finfet是将栅极长度减小到20 nm以下的关键。有了工艺流程和专利,才能保证未来在半导体市场的竞争力,这也是很多国际厂商翘首以待的主要原因。

1.《FinFET 多少年了,终于明白了FinFET与FD-SOI制程》援引自互联网,旨在传递更多网络信息知识,仅代表作者本人观点,与本网站无关,侵删请联系页脚下方联系方式。

2.《FinFET 多少年了,终于明白了FinFET与FD-SOI制程》仅供读者参考,本网站未对该内容进行证实,对其原创性、真实性、完整性、及时性不作任何保证。

3.文章转载时请保留本站内容来源地址,https://www.lu-xu.com/guonei/615115.html