分频器通常用于对给定的时钟频率进行分频,以获得所需的时钟频率。在设计数字电路时,经常使用各种不同频率的时钟脉冲,通常使用固定的晶体时钟频率来产生时钟分频所需的不同频率的时钟脉冲。

在FPGA设计中,分频器是频率较高的基础设计,在很多设计中,往往会用到芯片集成的PLL资源,比如使用Xilinx DLL和Altera PLL对时钟进行分频、乘法和移相。在一些时钟精度不高的场合,经常使用硬件描述语言来划分时钟源。

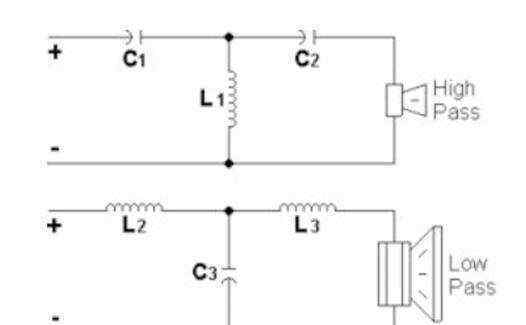

分频器是基本电路,一般包括数字分频器、模拟分频器和射频分频器。根据不同设计的需要,有时需要等占用率空。数字分频器采用计数器原理,其权重为分频系数。模拟分频器是一种分频器,通过带阻带通实现(例如音箱中带有高、中、低扬声器的分频器)。射频分频器也是一种滤波原理,通过带内带外衰减和阻抗匹配来实现。

随着FPGA技术的发展,基于FPGA技术的数字分频器硬件设计已经成为数字系统设计的研究热点。数字分频器通常分为整数分频器和小数分频器。在某些情况下,需要小数分频器。

本设计是基于FPGA的数字分频器。通过VHDL硬件设计语言,在Modelsim6.5上对所设计的分频器进行了仿真和验证

数字分频器的设计

数字分频器的设计不同于模拟分频器。数字分频器可以使用触发器设计电路来分频时钟脉冲。分频器的一个重要指标是空,即高电平脉冲在整个周期中所占的比例。空的比值通常需要不同的比值,如1:1,1: N等。因为空的比值要求不同的比值,所以采用的时钟分频原理也不同。在基于FPGA的数字分频器设计中,主要分为整数分频器、分数分频器和分数分频器。现在分别介绍整数分频器、分数分频器和分数分频器的设计。

永阳微波商城网上有各种分频器。

1.《分频器设计 分频器的简介》援引自互联网,旨在传递更多网络信息知识,仅代表作者本人观点,与本网站无关,侵删请联系页脚下方联系方式。

2.《分频器设计 分频器的简介》仅供读者参考,本网站未对该内容进行证实,对其原创性、真实性、完整性、及时性不作任何保证。

3.文章转载时请保留本站内容来源地址,https://www.lu-xu.com/fangchan/1585162.html