输入信号缓冲可以通过闭环单位增益运算放大器来实现,也是最常用的方式。对于低速ADC,不需要缓冲器或闭环运算放大器,而对于超高速ADC,如果不使用缓冲器,封装的寄生电感通常会降低输入信号的质量。在高速、高带宽的应用中,很难保证闭环运算放大器的稳定性。

缓冲器将提供强大的输入信号驱动,以避免多通道模数转换器交错时的相互影响。同时,它驱动大电容负载,并提供高质量的输入信号。因此,对于超高速ADC来说,输入信号缓冲器是最重要的模块之一。作为ADC的缓冲器,源跟随器的输出阻抗较低,结合ADC的采样电容可以达到宽带的目的。

硬件设计

常见的源跟随器有两种主要结构:单管源跟随器和超级源跟随器。

要求缓冲器的输出能够在一个周期内建立在0.5 LSB以内:

输入缓冲器的带宽满足:

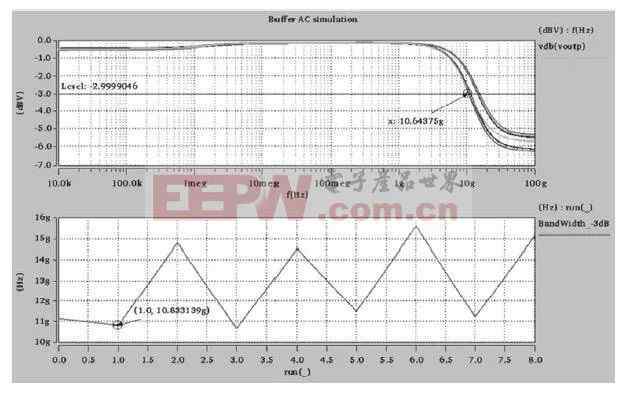

考虑工艺角度和温度变化对带宽的影响,取BW=7GHz。但实际时钟包含上升沿、下降沿和不重叠时间,建立时间不会达到一个周期,因此建立时间会短于一个时钟周期,所以设计采用带宽BW=10GHz。

模拟前验证

源极跟随器设计后,源极跟随器的负载电容为1.5pF,200mV的正弦输入信号通过4.7μF电容的交流耦合进入源极跟随器。图4示出了如图4所示的缓冲器在不同拐角下的带宽预模拟(最小SSHT为10.8GHz)。

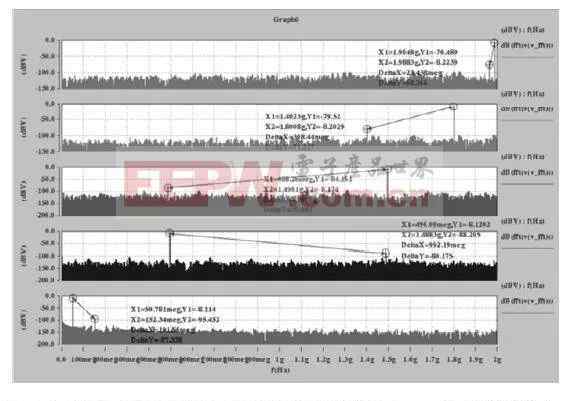

通过FFT分析源跟随器的输出,得到不同工艺角度下源跟随器输出的线性度(SFDR),如表1所示。

从前面的仿真可以看出,所设计的缓冲器在低频时线性度在85dB以上,在1.8GHz输入信号时线性度在71dB以上,满足12位4GSPS ADC的应用要求。

模拟后验证

源极跟随器经过预仿真验证后,实现版图,提取寄生参数,完成后仿真验证。图5示出了在不同输入信号频率下源跟随器在TT角下的输出信号的频谱,从中可以获得SFDR参数。不同拐角的统计结果如表2所示。与前仿真相比,后仿真的线性度有一定程度的降低,最小带宽大于9.6GHz,均满足12位4GSPS ADC的要求。

作者信息

胡,,电子科技大学微电子与固态电子学院。

1.《高速缓冲器 一种用于超高速ADC的输入信号缓冲器设计?》援引自互联网,旨在传递更多网络信息知识,仅代表作者本人观点,与本网站无关,侵删请联系页脚下方联系方式。

2.《高速缓冲器 一种用于超高速ADC的输入信号缓冲器设计?》仅供读者参考,本网站未对该内容进行证实,对其原创性、真实性、完整性、及时性不作任何保证。

3.文章转载时请保留本站内容来源地址,https://www.lu-xu.com/jiaoyu/1227104.html